- -A masked Rom, 81 simply ROM is preoficermed with data as the chip is fabricated.

These chips are useful for consumer appliances, where loage number of write are produced and once installed, data will not be charged.

- A PROM is a powofiammable ROM. PROM coun be powofiammed by the user with any standard PROM powofiammer. Rather than being hand-wired the PROM trees a series of intermal connections similar to fuses. Powofiamming data into the PROM essentially blows the proper fuses so that each world of membry stones the connect value.

- An EPROM is an esvasable PROM.

EPROM can be posogrammed like a PROM but its contents can be esused and the chip supprogrammed.

Psvogramming an EPROM is similar to charging capacitous. The charged and uncharged capacitous cause each world of membry to solbre the consect value. The chip is enased by being placed under utbraviolet light causes the capacitous to leak their charge, thus resetting the chip's contents.

- EEPROM, sometimes denoted E<sup>2</sup>PROM, is an electrically erasable PROM. It works like an EPROM, except its contents and crassed and repropogrammed electrically, nather than by using ultraviolet light.

COMPUTER ORGANIZATION AND ARCHITECTURE

UNIT-I

- In EPROM, it must be entirely enased and then supprogrammed, but in E2PROM it is possible to modify individual locations of the EEPROM while leavings other locations unchanged.

- One common use of EEPROM is basic input/output system & BIOS of poisonal computer.

-> A Special type of EEPROM called a flashEEPROM is electorically espasable in blocks of date, nather than individual locations.

- The excternal configuration of all Rom types is

A chip with 2" words, each having m bits, has n address ilps, An-1 to Ao and m data offs Dm-1 to Do. It also have this enable input (CE) Both must succeive high (logic i) signals if the and an output enable (OE). chip is to output data;

=> RAM Chips

RAM chips are difficulated by how they maintain their data.

Dynamic RAM / DRAM Static RAM / SRAM.

- DRAM chips age like leaky capacitors. Initially data is stored in the DRAM chip chooging its membry cells to their maximum values. The change slowly leaks out and would eventually go too locompoter organization and architecture must data => Internal chip organisation:

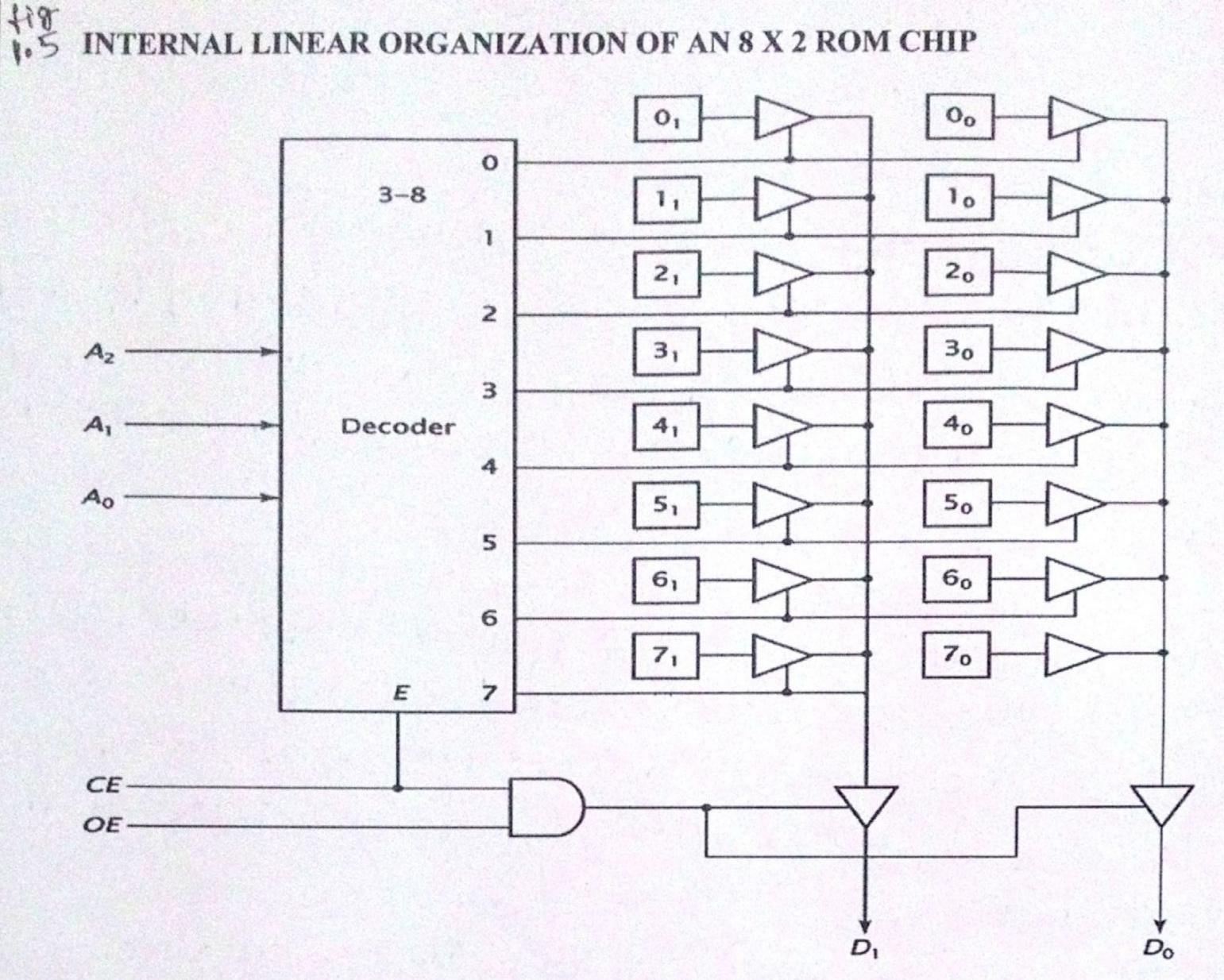

-The intermal organizations of Rom and RAM chips are similar.

- To illustrate the simplest organization, a lineage organization consider an 8x2 Romchip. [fig 1.5] - Chiphas 3 address i/p & 2 data outputs and 16 bits of internal storage aronanged as eight 2-67

- The there address bits are decoded to select one of the eight locations, but only if chip enable (CE) is author If CE=0, the decoder is disabled and no location is selected. The paistate buffers for that locations cells are enabled, allowing data to pass to the autput buffers.

If both CELOE are set to 1, these buffers are enabled and the data is output from the chip; otherwise the autputs are tai stated.

Assume 2 bit locarmy Az AI AD NO olp/highimpedance.

### INTERNAL LINEAR ORGANIZATION OF AN 8 X 2 ROM CHIP

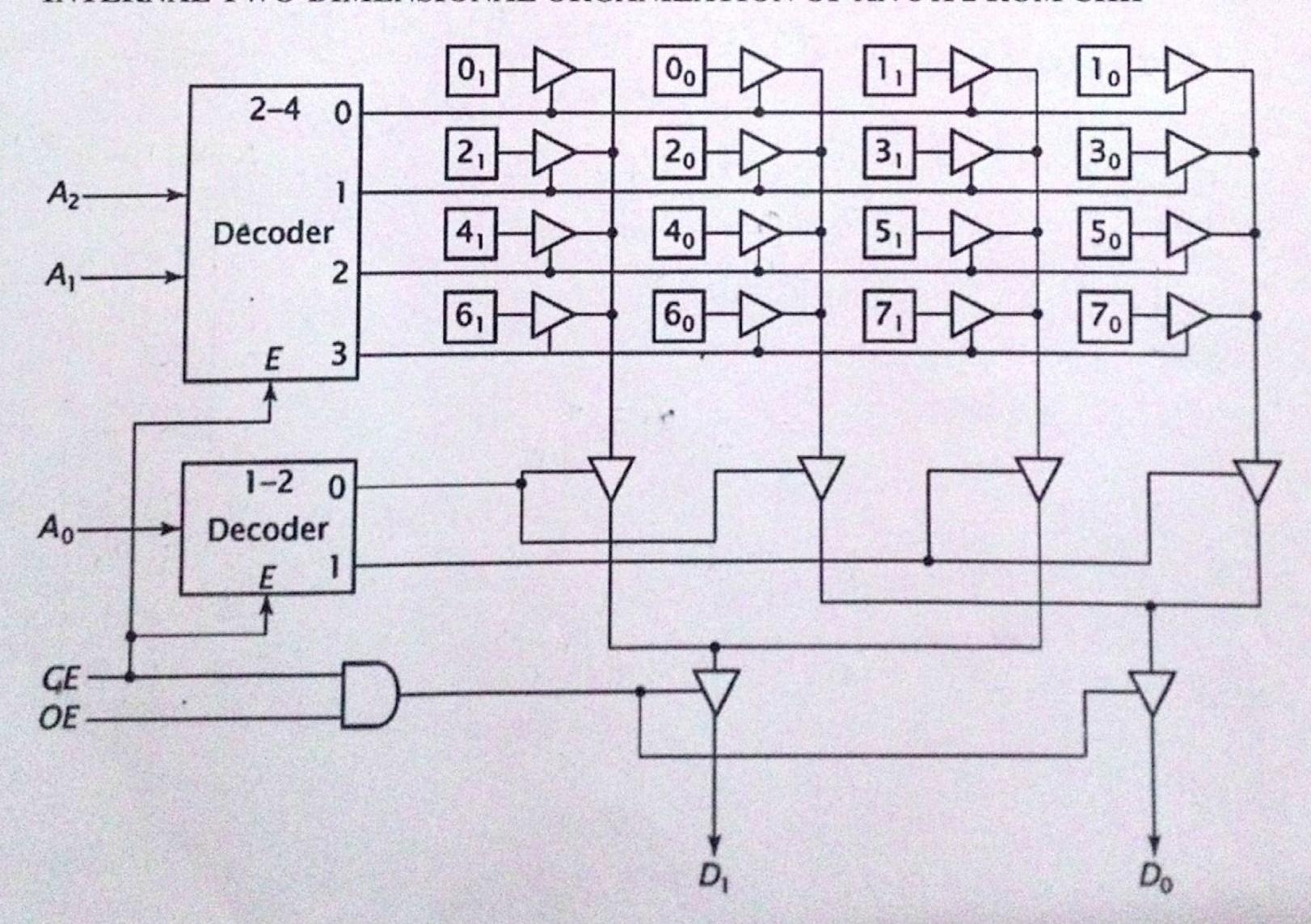

#### tig INTERNAL TWO-DIMENSIONAL ORGANIZATION OF AN 8 X 2 ROM CHIP

# - Internal Chip Organization: -

- As the number of locations increases, the size of the adobess decoder reeded in a linear organisation becomes perchibitively laage.

- To solve this phoblem, the memby chip can be designed

using multiple dimensions of decoding.

- Consider the two-dimensional organization of the Same 8x2 Rom chip (fig 1.6)

- This configuration have four nows with four bits pen now; each now holds two data values.

- The two high-order address bits of the two locations in each now one the same. These two high biden address bit select one of the foren nows, and the low- biden address bit selects one of the two locations in the now.

AZ A1 A0 0 0 0

when AO = 0 then the locatrons 0, 2, 4,6 ane selected

0 0 1 0 1 0 when A0 = 1 , 3, 5, 7 locatrons are selected.

0 1 1 1 0 0

1 0 1

1 10

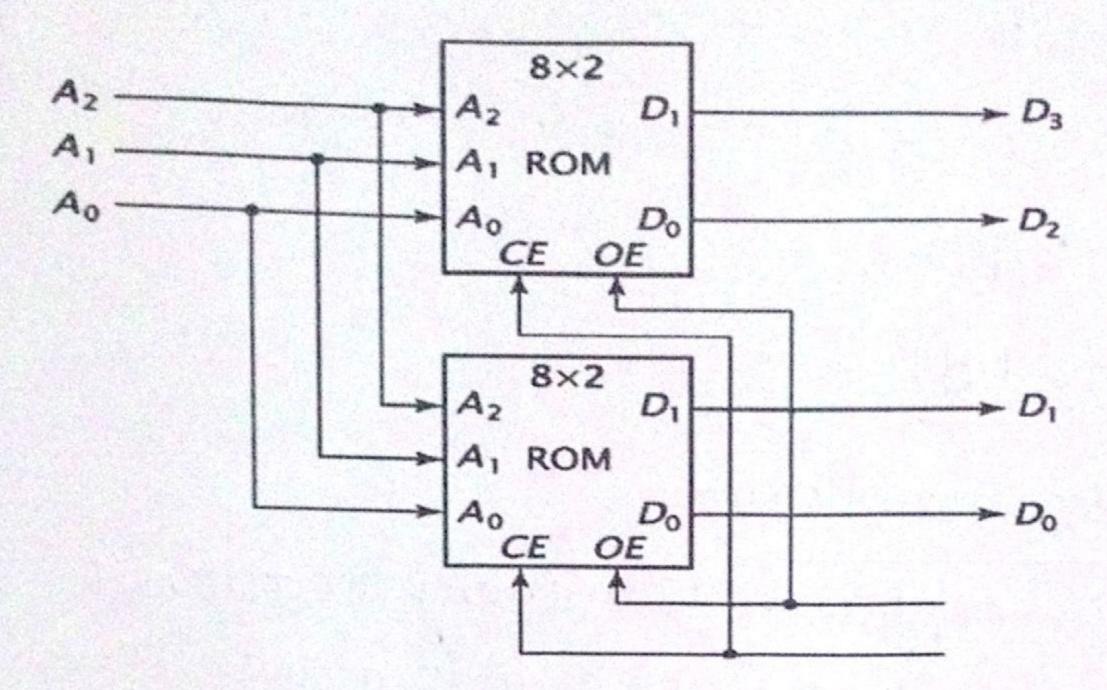

# => Memay subsystem Configuration:-

- Two & more chips can be combined to careate membry with more bits per location.

- This is done by connecting the corresponding address and control signals of the chips, and connecting their data pins to different bits of the data bies.

- For esa, two 8x2 chips can be combined to create

# Fig 107

- Both chips succeive the same thorse address inputs from the bus, as well as the same chip enable and output enable signals.

The date pins of the first chip are connected to bits 3 and 2 of the data bus, and those of the other chip are connected to bits 1 and 0.

- When the CPU seads dater, it places the address on the address bus.

- Both chips head in address bits Az, A, Ao and perform their internal decepting.

- If the CE and OE signals are activated the chips output their data onto the four bits of the data bus.

Since the address and enable signals are the same for both chips, they act as a single 8x4 chip.

### AN 8 X 4 MEMORY SUB SYSTEM CONSTRUCTED FROM TWO 8 X 2 ROM CHIPS

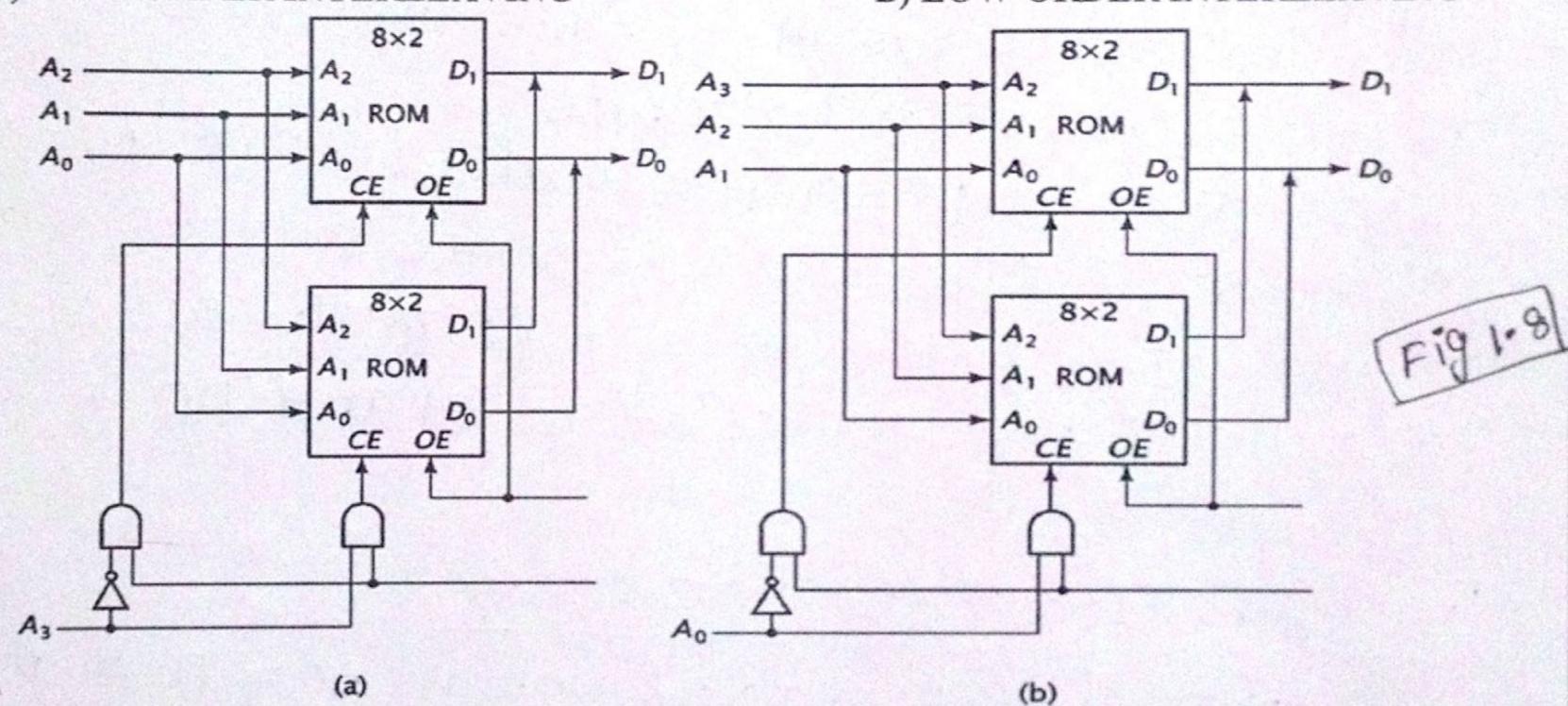

A 16 X 2 MEMORY SUBSYSTEM CONSTRUCTED FROM TWO 8X2 ROM CHIPS WITH A)HIGH-ORDER INTERLEAVING

B) LOW-ORDER INTERLEAVING

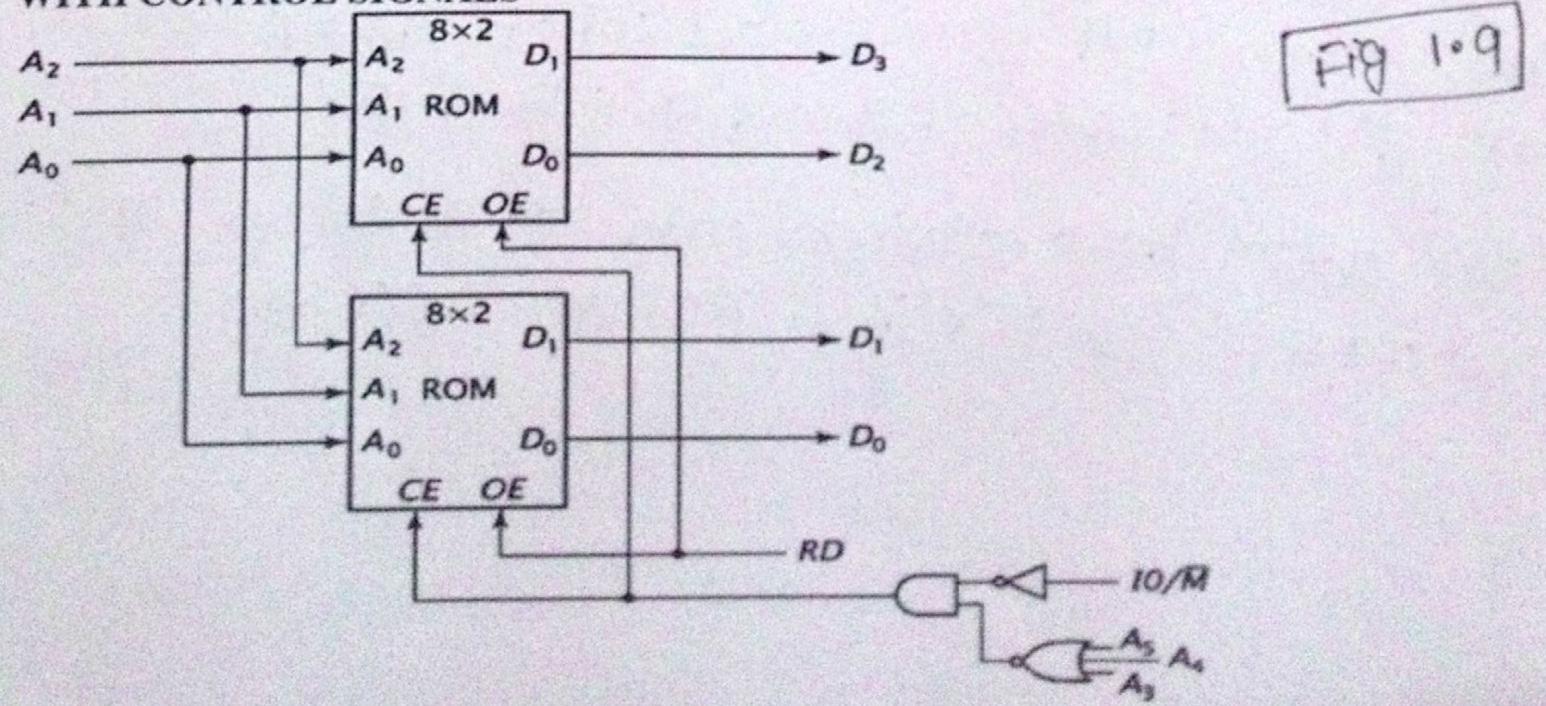

AN 8X4 MEMORY SUB SYSTEM CONSTRUCTED FROM TWO 8X 2 ROM CHIPS WITH CONTROL SIGNALS

COMPUTER ORGANIZATION AND ARCHITECTURE

UNIT-I

Instead of caeating wider woods, chips can be combined to caeate more woods.

- The 8x2 chips could be used to configure a 16x2 membry subsystem.

## F9 1.8

Fig 1.8 a - High-conden Interleaving

The upper chip is configured as membry locations ore 0 to 7 (0000 to 0111) and lower chip locations are 8 to 15 (1000 to 1111). The upper chip always has A3=0 and lower chip has A3=1. This difference is used to select one of the two chips.

-when A3=0 upper chip is enabled & lower chip-district—when A3=1 upper chip-disabled lower chip-enabled.

-Since both chips corresponds to the same date bits, both are connected to D1 and D0 of the

[Pig 1.8 b] - Low-Order Interleaving

- -The upper chip is enabled when A0 = 0 81 by addresses XXXO, in this case 0, 2, 4,6,8,10,12 & 14.

The lower chip is enabled when A0 = 1, which is true for addresses 1,3,5,7,9,11,13 & 15.

- Low- order interleaving can offer some speed advantages for pipelined membry access.

## 2 Input logic for CE & OE:

- The CPU generally outputs a control signal called RD 81 RD', which it sets active when it wants to seed data from membry. This signal is sufficient to doine OE.

- The CE signal makes use of the unused address bits.

Assume that the 8x4 membry is used in a system with a 6-bit address bus. Assume this chip consesponds to locations 0 to 7 (00 0000 to 00 011).

Address bits As, A1 and A0 select a location within the membry chips; bits As, A4, A3 must be 000 for the chips to be active.

The fig includes the IO/M signal that is supplied by processors that use isolated I/O.

Multibyte Data Organization:

There are two commonly used organizations for multibyte data: big endian

Little endian

- In big endian format, the most significant byte of a value is stolled in location X, the following byte in location X+1, and so on

location X+1, and so on

- In little endian, the order is suverised. The least significant byte is stolled in location X, the next significant byte is stolled in location X, the next byte in location X+1 and so on.

Eg: F81 ex, the hexadecimal value 01020304H organized in big endian & little endian formatts as follows.

| Membry | Date(in Hex) |

|--------|--------------|

| 100    | 01           |

| 10.1   | 02           |

| 102    | 03           |

| 103    | 04           |

| Membly<br>Address | Data (in Hea) |

|-------------------|---------------|

| 100               | 04            |

| 101               | 03            |

| 102               | 02            |

| 103               | 01            |

| Little            | endian-       |

- The main problem comes in transferring date between computers with different organizations.

- one other issue for multibyte wollds is alignment.

modern microprocesses can head in more than one byte of data at a time.

Alignment simply means storing multibyte values in locations such that they begin at a location that also begins a multibyte head block.