# LO SUBSYSTEM ORGANIZATION AND INTERFACING

- cou treate membry as homogeneous.

- I/O devices are very different. A PC Keyboard a hoord disk perform different function, yet both are part of the I/O subsystem.

- Each I/O device is connected to system buses. Each I/O device includes I/O interface circuitary, actually this circuitary interacts with the busest also interacts with the busest

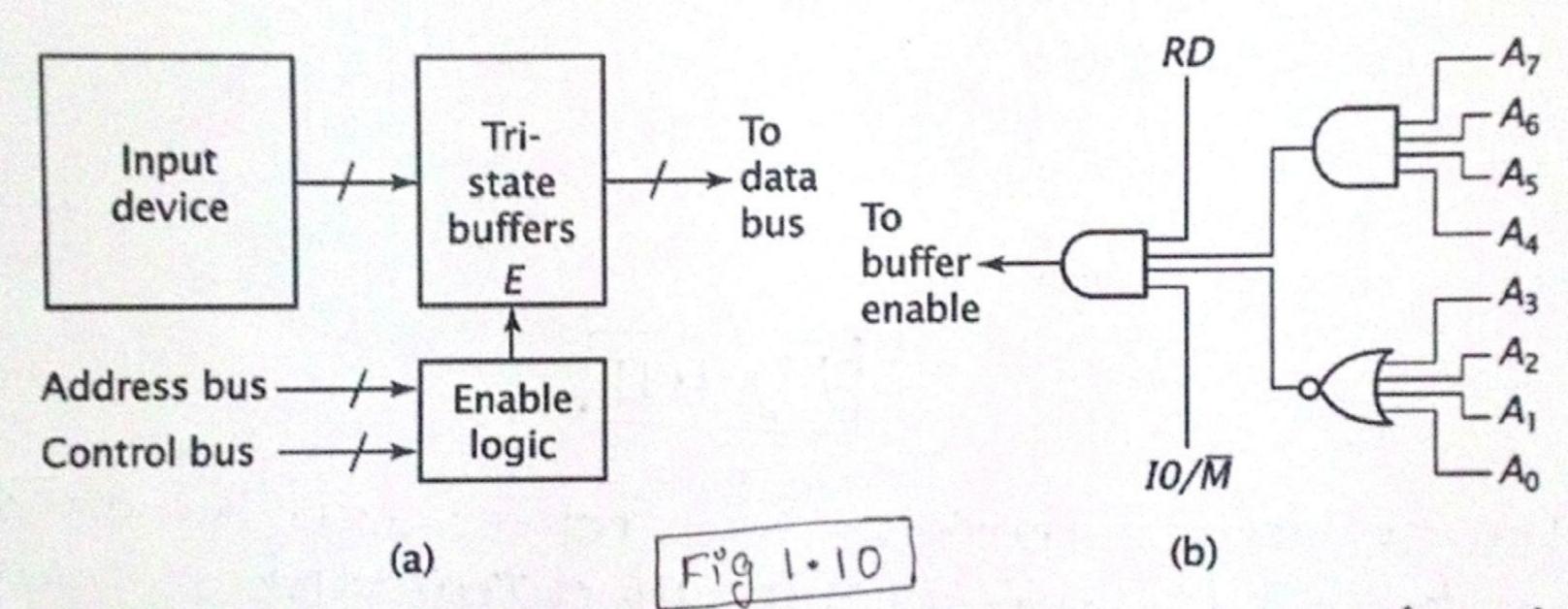

AN INPUT DEVICE: A) WITH ITS INTERFACE B) THE ENABLE LOGIC FOR THE TRI-STATE BUFFERS

The above fig [fig 1.10] shows the generic intervale concurry

for an input device such as a keybaand.

- The data from ilp device goes to toussaite buffer. when the values on the address bus & control bus one charct the buffers are enabled and date pases onto data bus - When this values agre not cognect logic block does not enable the buffers; they agre toristated and donot place data onto

- The key to this design is enable logic. Each I/o device has unique address. The enable logic must not enable the buffegres unless it neceives the coonect address from the address bus. It must also get cosonect contol signals from control bus. For an i/P dwice RD signal must be assented as well as IO/M signal

- Fig 1.10a shows the enable logge for an ilp device at 1111 0000 con computer system with an 8 bit address

COMPUTER ORGANIZATION AND ARCHITECTURE

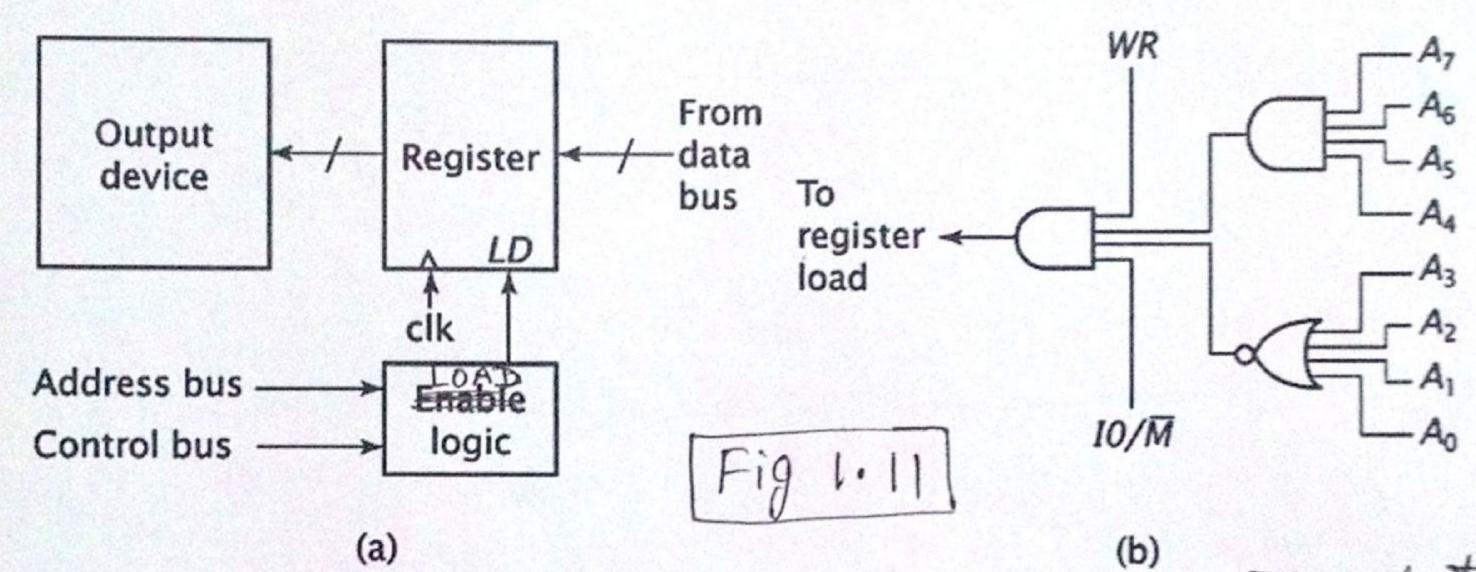

> F81 this tou state buffers are replaced with registers

or shown in [fig 1.11a].

The tou-state buffers are used in i/polivice interfaces to make sure that no more than one device writes

data to the bus at any time.

UNIT-I

### AN OUTPUT DEVICE: A) WITH ITS INTERFACE B) THE LOAD LOGIC FOR THE REGISTER

> FOI of p devices buffers are not needed. The data can be made available to all output devices; only the device with correct address will read it in.

- When the logic receives convect signals, it asserts the LD signal of the hegister causing it to head data from the register at its leisure.

The logic to generate the load signal for an off the logic to generate the load signal for in Fig 1.11b dwice at address 1111 0000 is shown in Fig 1.11b

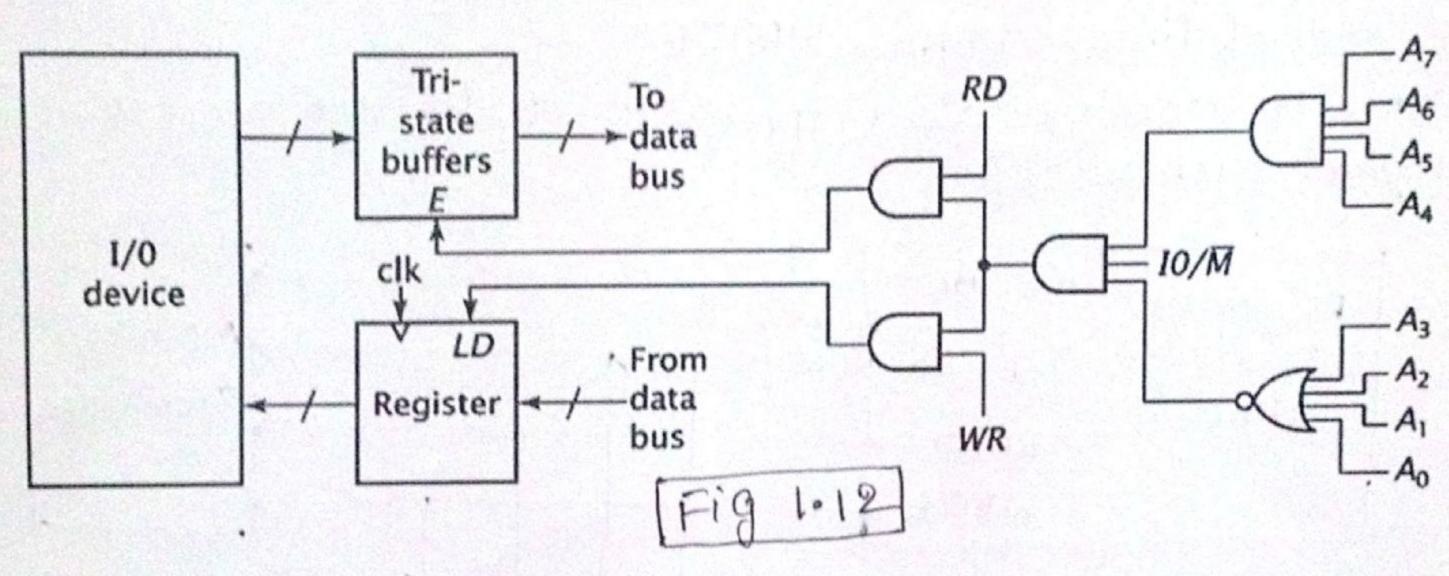

> Some devices are used for both input & output. Eg: - Hand disk.

- such devices requires a combined interface; one for ilp

and the other for output.

- The following figure shows a combrida I/o interface for address IIII 0000.

### A BIDIRECTIONAL INPUT/OUTPUT DEVICE WITH ITS INTERFACE AND ENABLE/LOAD LOGIC

- I/o devices age much slower than CPUS and memory. For this meason, they can have timing poroblems when interacting with the CPU. Most cpus have

a control input signal READY.

- The externa clock cycles generated by having READY setlow agre called wait states.

-These I/o interfaces are fine for small computers, such as microwave oven controllers, but not suitable 181 Large Computers.

Many systems use interoupts so they can perform useful work while waiting for the much slower

- These Ito interfaces are also not suited to large date transfers. Direct Menby Acces (DMA) is another date transfers. The CPU in these transfers, thus performing used to by COMPUTER ORGANIZATION AND ARCHITECTURE MICKLY.

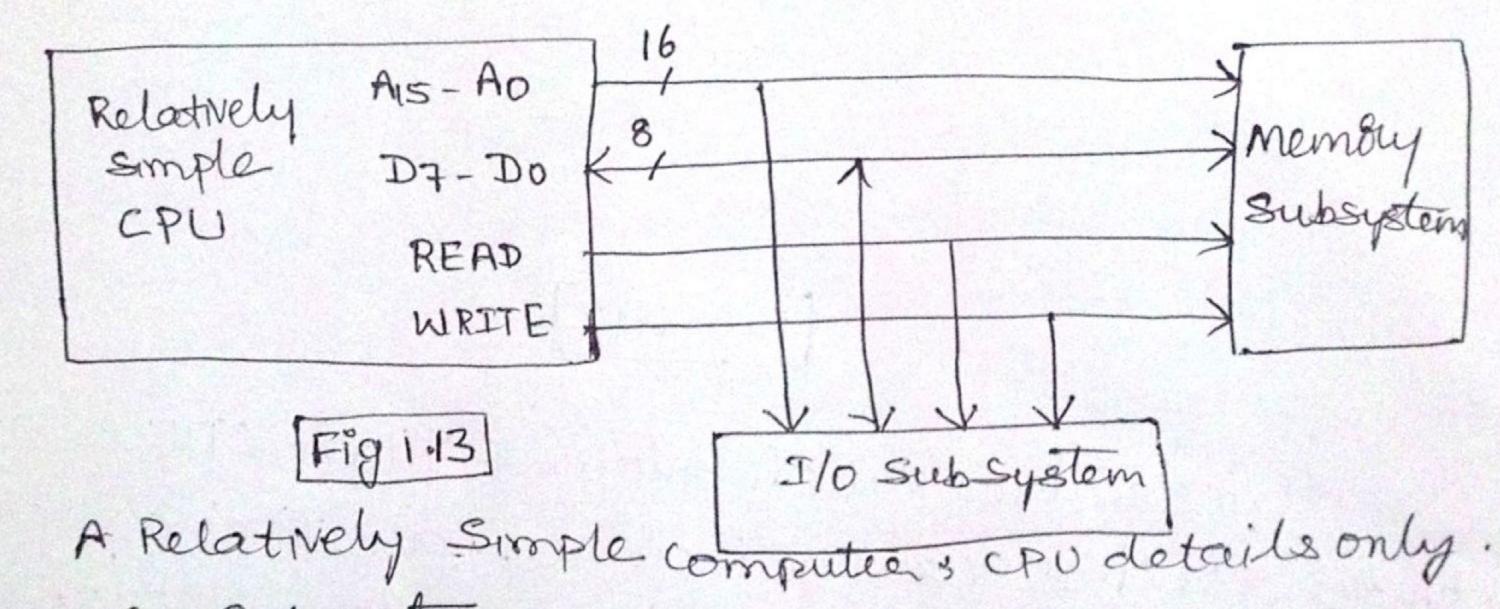

# > A Relatively Simple Computer

- Consider a sample computer, that have 8K of RAM. It will also have a membry mapped, bidirectional I/o part at addouss 8000H.

+181 16 bit adobresses - 16 adobress pros - A 15 to Ao - data thorough D7 to Do, data pms.

te contoil lines READ & WRITE.

t-since it uses memory mapped Ilo, it does not need a control Signal such as IOTA.

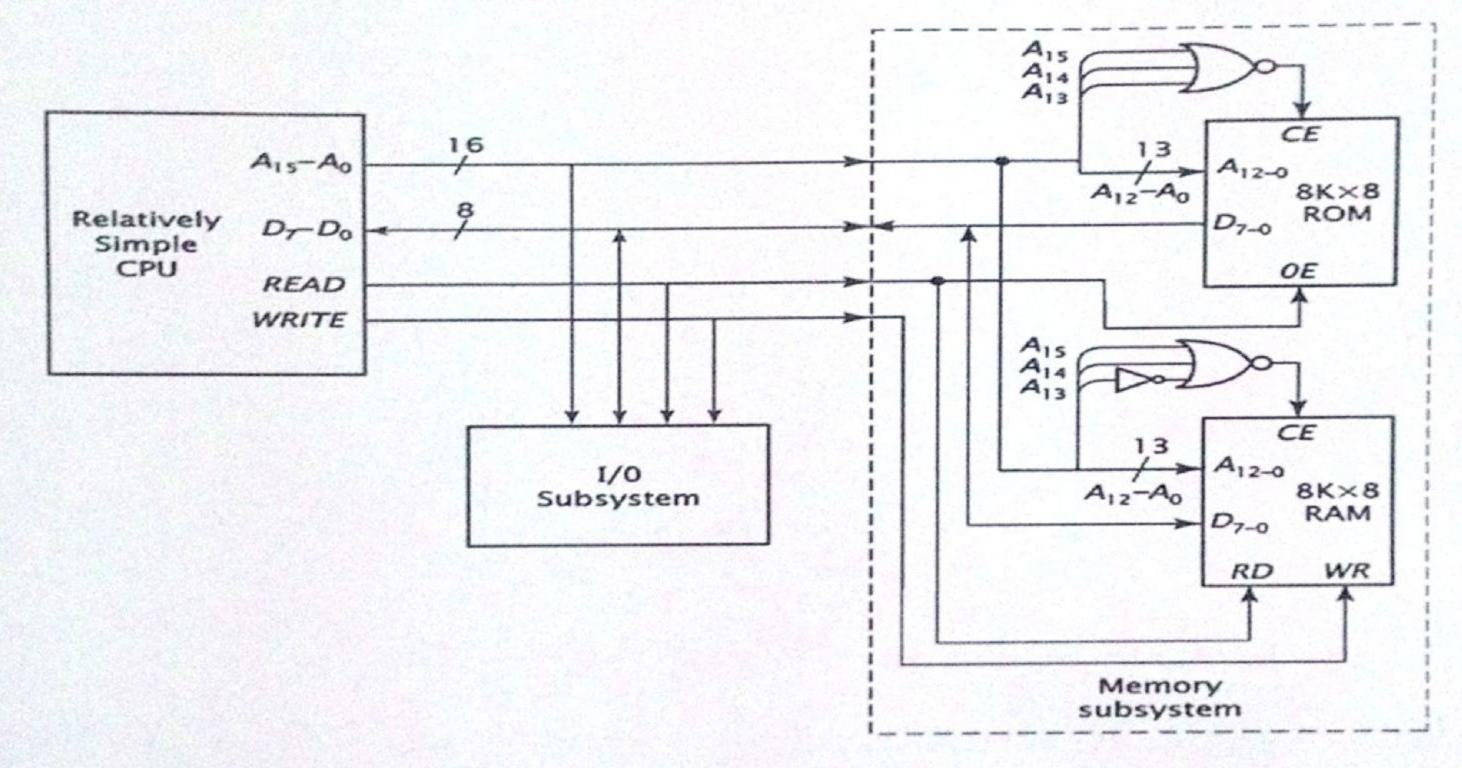

Memby Subsystem:-- ROM contains address in the sunge o 0000 0000 0000 0000 to 0001 1111 1111 The 8K RAM immediately follows the Rom and has address

To access a memby chip, the processor must supply on address used by the chip, as well as the proper contoal signals.

To access a memby-chip, the phocesson must supply an address used by the chip

- An 8 K membry chip how 213 internal membry locations. - It has 13-bit address input to select one of these

Locations. (A12 to A0 address bits).

-The sumaining 3 bits (AIS, AI4, AI3) will be used to select one (8) neither) of the membry.

## FIG 1.14 A RELATIVELY SIMPLE COMPUTER: MEMORY SUBSYSTEM DETAILS

- The top there address bits of Rom chip are 000 for all

addresses.

- Similarly the RAM Chip is enabled when AISAILAB = 001.

- Read signal is connected to ROM'S OE.

- ROM chip outputs date when CELOE agreenabled.

- The RAM has two control inputs, RD and MR. The READ and WRITE signals from the control bus can doive these two signals

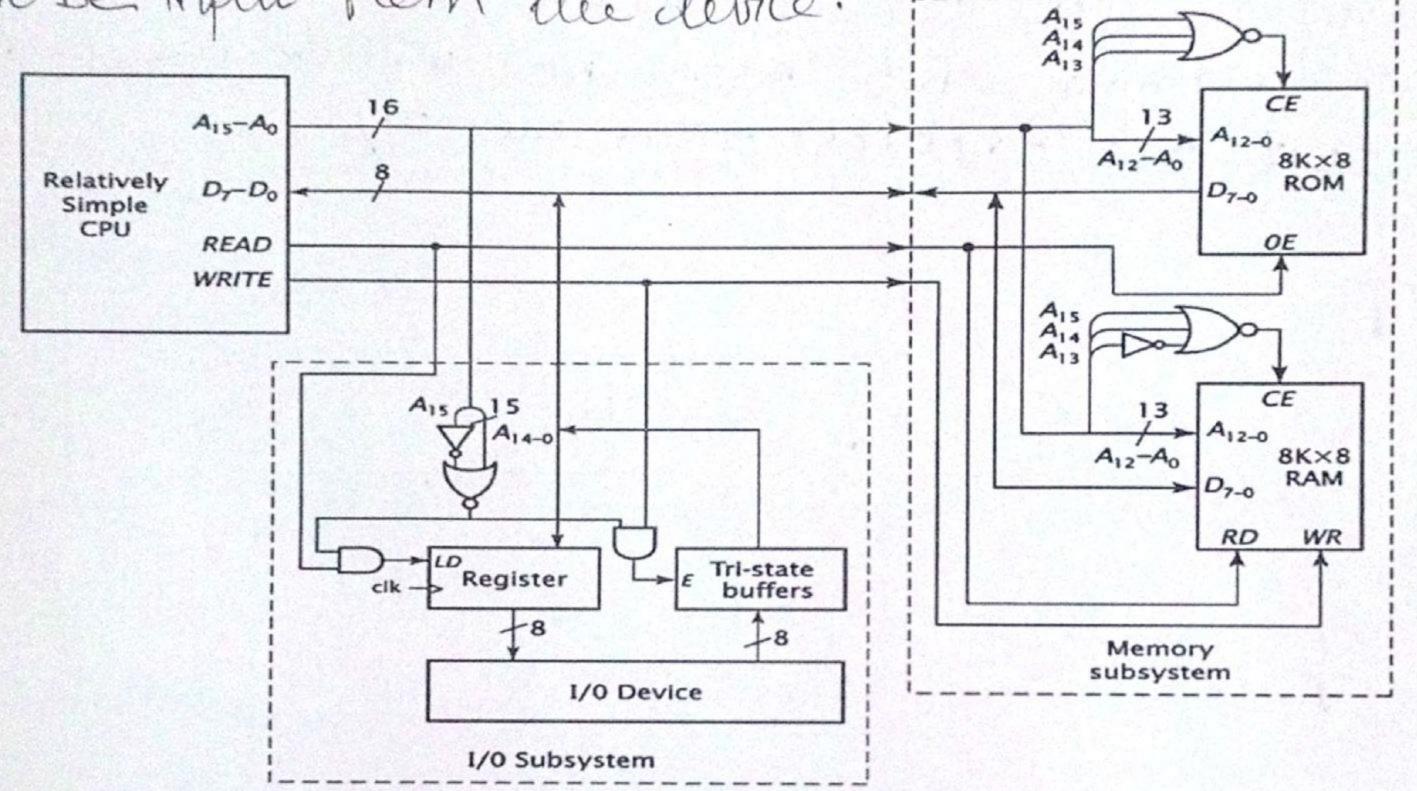

> I/o Subsystem:

- The system specifies one bidiaectional I/o poot at address 8000H 81 1000 0000 0000 0000 in binary.

- we use the adobcess and the control signals to enable the i/p 2 o/p interface circuitry for this port.

COMPUTER ORGANIZATION AND ARCHITECTURE

- We use a gegister to store data output to the device and trie-state buffers to pass throughdates to be input from the device.

Fig 1 . 15 A RELATIVELY SIMPLE COMPUTER: FINAL DESIGN

- we need to design the address logic 80 that it succeptizes 8000 H.

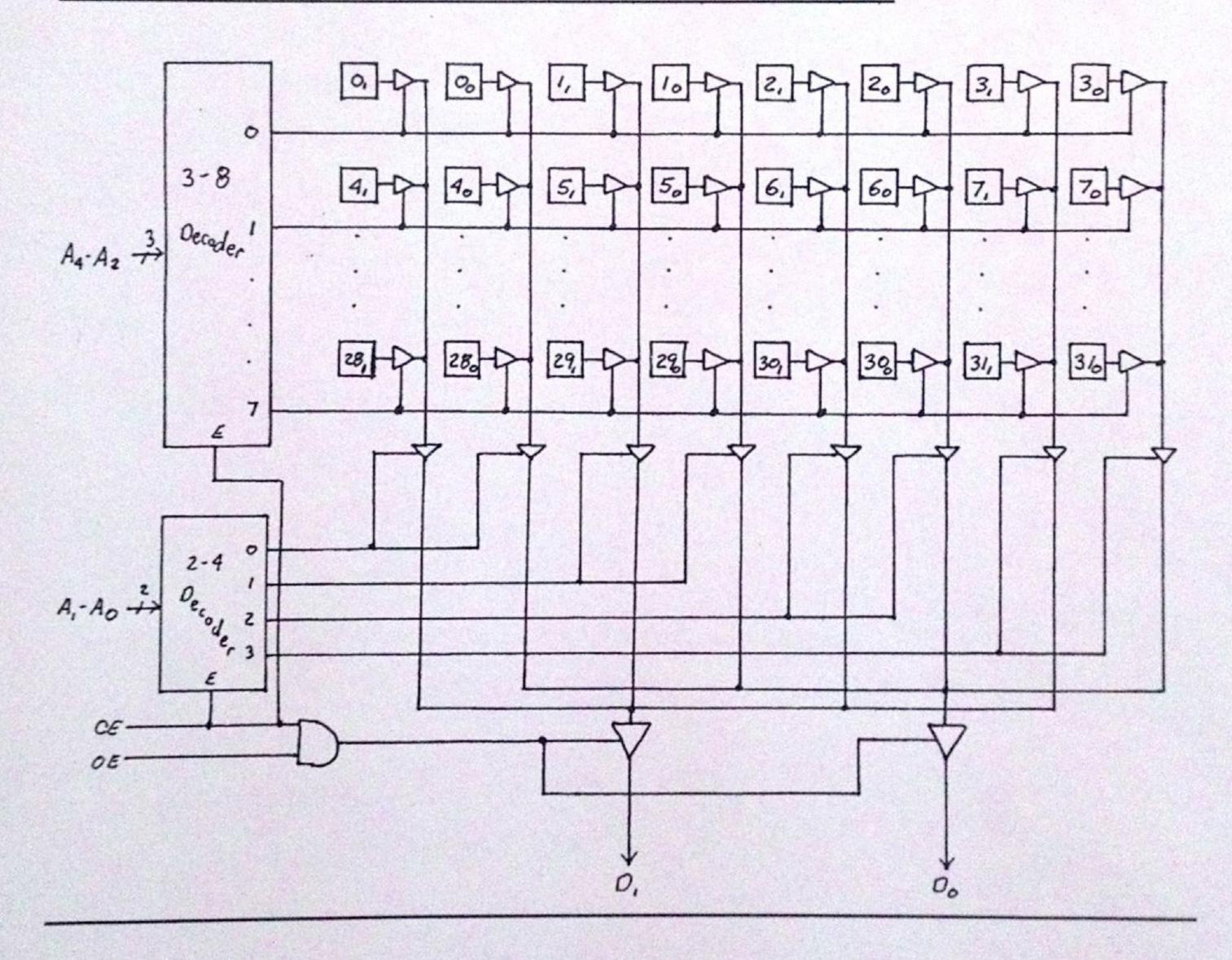

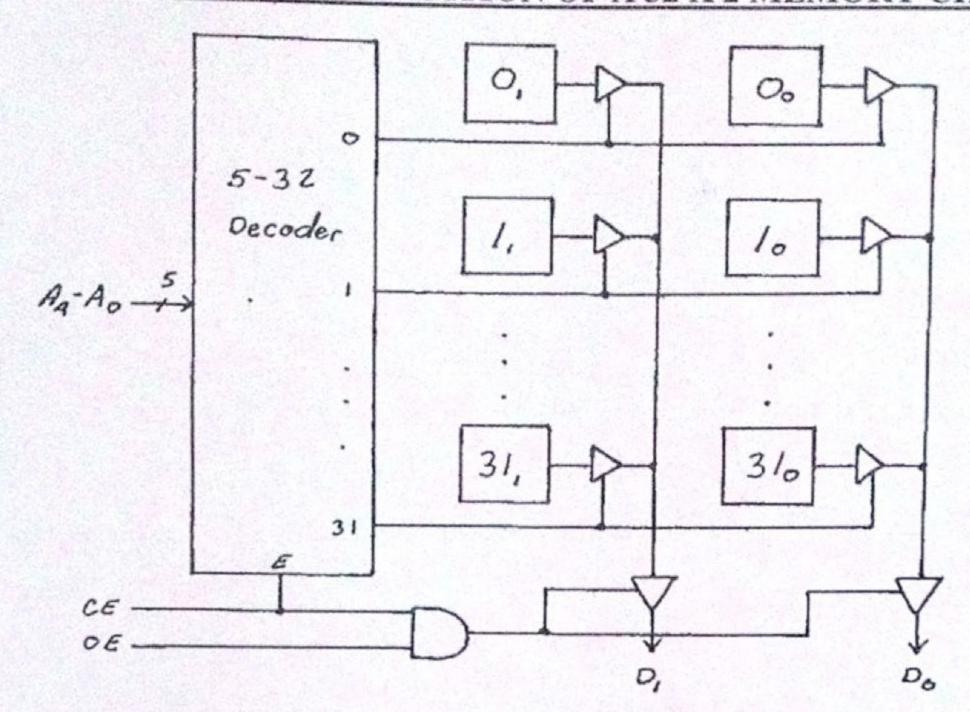

# INTERNAL LINEAR CONFIGURATION OF A 32 X 2 MEMORY CHIP

### INTERNAL 2-D CONFIGURATION OF A 32 X 2 MEMORY CHIP